浅槽隔离

浅槽隔离,即 shallow trench isolation,简称STI。通常用于0.25um以下工艺,通过利用氮化硅掩膜经过澱积、图形化、刻蚀硅后形成槽,并在槽中填充澱积氧化物,用于与硅隔离。

基本介绍

- 中文名:浅槽隔离

- 外文名: shallow trench isolation, STI

- 适用工艺:半导体工艺

内容简介:

浅槽隔离(Shallow Trench Isolation;STI)技术製作主动区域之间的绝缘结构已逐渐被普遍採用。STI结构的形成通常是先在半导体基底上沉积一层氮化硅层,然后图案化此氮化硅层形成硬掩膜。接着蚀刻基底,在相邻的元件之间形成陡峭的沟渠。最后,在沟渠中填入氧化物形成元件隔离结构。虽然STI工艺比LOCOS工艺拥有较佳的隔离特性,然而由于电浆破坏,可产生大量的蚀刻缺陷,且具有尖锐角落的陡峭沟渠也会导致角落寄生漏电流(Corner Parasiticleakage),因而降低STI的隔离特性。

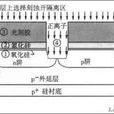

用于亚0.25um工艺的选择性氧化的主要技术是浅槽隔离(STI)。STI技术中的主要绝缘材料是澱积氧化物。选择性氧化利用掩模来完成,通常是氮化硅(Si3N4)。掩模经过澱积、图形化。刻蚀硅后形成槽。在掩模图形暴露的区域,热氧化150~200Å厚的氧化层之后,才能蚀硅形成槽(如图1所示)。这种热生长的氧化物是硅表面钝化,并且可以使浅槽填充的澱积氧化物与硅相互隔离。它还能作为有效的阻挡层,避免器件中的侧墙漏电流产生。

图1 STI氧化硅衬层

图1 STI氧化硅衬层在0.25um和以下的技术节点中,浅槽隔离(STI)技术被广泛套用。STI取代LOCOS的原因有如下几点:

(1) 更有效的器件隔离的需要,尤其是对DRAM器件而言;

(2) 对电晶体隔离而言,表面积显着减小;

(3)超强的闩锁保护能力;

(4) 对沟道没有侵蚀;

(5) 与CMP的兼容。

在基本的STI工艺中(如图2所示),利用乾法刻蚀在硅片表面可以刻出深0.3~0.8um的沟,这些沟有直角和圆角。STI沟的深宽比大约在2:1~5:1,由于DRAM器件对漏电流的敏感,需要更高的深宽比。隔离沟表面生长有线性的氧化层,用CVD氧填充,并利用CMP来平坦化。STI较LOCOS技术成本更高,因为需要更複杂的工艺步骤。然而,STI的优点足以弥补成本高的问题。

图2 浅层隔离

图2 浅层隔离工艺步骤:

槽刻蚀

- 隔离氧化层。硅表面生长一层厚度约150埃氧化层;可以做为隔离层保护有源区在去掉氮化物的过程中免受化学沾污。

- 氮化物澱积。硅表面生长一薄层氮化硅:a)由于氮化硅是坚固的掩膜材料,有助于在STI氧化物澱积过程中保护有源区 b)在CMP时充当抛光的阻挡材料。

- 掩膜,浅槽隔离

- STI槽刻蚀。在经过上面的光刻之后把没有被光刻胶保护的区域用离子和强腐蚀性的化学物质刻蚀掉氮化硅、氧化硅和硅。需要注意的是会在沟槽倾斜的侧壁及圆滑的底面有助于提高填充的质量和隔离结构的电学特性

氧化物填充

- 沟槽衬垫氧化硅

硅片再次清洗和去氧化物等清洗工艺后,高温下在曝露的隔离槽侧壁上生长150埃的氧化层,用以阻止氧分子向有源区扩散。同时垫氧层也改善硅与沟槽填充氧化物之间的界面特性 - 沟槽CVD氧化物填充

氧化物平坦化

- 化学机械抛光

- 氮化物去除

工艺优点:

- 更有效的器件的需要,尤其是对DRAM器件而言。

- 对电晶体隔离而言,表面积显着减小。

- 超强的闩锁保护能力。

- 对沟道没有侵蚀。

- 与CMP的兼容。

读书笔记摘抄新闻资讯

读书笔记摘抄新闻资讯