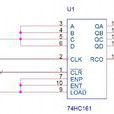

74HC161

74HC161和74LS161都是常用的四位二进制可预置的同步加法计数器,74HC161是CMOS型,74LS161是TTL型。它可以灵活的运用在各种数字电路,以及单片机系统中实现分频器等很多重要的功能。

基本介绍

- 中文名:同步二进制计数器

- 名称:74HC161

- 数据输入端:D,C,B,A,

- 数据输出端:Q0~Q3

- 同步置数:LOAD的反

- 异步清零:CLR的反

为异步清零控制端

为同步置数控制端

ENP,ENT为计数控制端

D , C , B , A 为并行数据输入端

Qd,Qc,Qb,Qa 为数据输出端

RCO为进位输出端

CLK为时钟输入端

输入 | 输出 | ||||||

|  | ENP | ENT | CLK | D,C,BA | Qd~Qa | RCO |

0 |  |  |  |  |  | 0000 | 0 |

1 | 0 |  |  |  | d,c,b,a | d,c,b,a | |

1 | 1 | 1 | 1 |  |  | 计数 | |

1 | 1 | 0 |  |  |  | 保持 | |

1 | 1 |  | 0 |  |  | 保持 | 0 |

74hc161的主要功能如下:

- 异步清零功能:当CLR的反为零时,不论有无时钟脉冲CLK和其他信号输入,计数器被清零,即Qd~Qa都为0。

- 同步并行置数功能:当CLR的反=1,LOAD的反=0时,在输入时钟脉冲CLK上升沿的作用下,并行输入的数据dcba被置入计数器,即Qd~Qa=dcba。

- 计数功能:当LOAD的反=CLR的反=ENP=ENT=1,当CLK端输入计数脉冲时,计数器进行二进制加法计数

- 保持功能:当LOAD的反=CLR的反=1时,且ENP和ENT中有”0“时,则计数器保持原来状态不变。

读书笔记摘抄新闻资讯

读书笔记摘抄新闻资讯