arm cortex a5

ARM Cortex™-A5是性价比最高的处理器解决方案,高性能低成本并且支持双核技术。

基本介绍

- 中文名:arm cortex a5

- 外文名:arm cortex a5

- 内容:Cortex-A系列处理器

- 优点:高性能低成本并且支持双核技术

简介

Cortex-A5与Cortex-A7、Cortex-A8、Cortex-A9以及Cortex-A15同属于Cortex-A系列处理器。ARM Cortex™-A5是性价比最高的处理器解决方案,高性能低成本并且支持双核技术。能够向最广泛的设备提供 Internet 访问:从入门级智慧型手机、低成本手机和智慧型移动终端到普遍採用的嵌入式、消费类和工业设备。

性能规格参数

| ARM Cortex-A5 性能、功耗和面积 | ||

|---|---|---|

工艺类型/额定电压 | 低泄漏,1.1V | 性能,1.0V |

性能或频率最佳化 | 频率 | 频率 |

频率 | 530~600 MHz | >1GHz |

面积,不包括 RAM/高速快取 | 0.27mm2 | 0.27mm2 |

面积(带 16K/16K 高速快取) | 0.53mm2 | 0.53mm2 |

面积(带 16K/16K 高速快取 + NEON) | 0.68mm2 | 0.68mm2 |

动态功耗 | 0.12 mW/MHz | <0.08mW/MHz |

能效 | 13 DMIPS/mW | >20 DMIPS/mW |

核心面积、频率範围和功耗主要取决于工艺、库和最佳化情况。

上面引述的数字说明了使用通用工艺技术、ARM 标準单元库和 RAM 的合成核心的性能。

ARM 高性能 SC12 逻辑库和性能 RAM

频率最佳化

85% 使用率

慢硅/Vdd-10% (1.0V)/125C 情况下的频率

10% OCV 和 50ps 时钟偏差

标準硅/Vdd (1.1V)/25C 情况下的功耗

所有额定电压电晶体

| Cortex-A5 | |

|---|---|

Dhrystone 性能 | 每个核心 1.57 DMIPS/MHz |

多核 | 1-4 个核心 还提供单核版本 |

ISA 支持 | ARM Thumb®-2 / Thumb DSP & SIMD 扩展 VFPv3 浮点(可选) NEON™ 高级 SIMD (可选) Jazelle® DBX 和 RCT |

记忆体管理 | ARMv7 记忆体管理单元 |

调试和跟蹤 | CoreSight™ DK-A5 |

| Cortex-A5 主要功能 | |

|---|---|

Thumb-2 技术 | 可为传统 ARM 代码提供最高性能,对于存储指令占用的记忆体,最多可节省 30% 的空间。 |

TrustZone® 技术 | 确保全全套用的可靠实现,适合从数字着作权管理到电子支付等套用。获得技术和行业合作伙伴的广泛支持。 |

NEON 媒体处理引擎 (MPE) | 可选 Cortex-A5 NEON 可提供 Cortex-A5 浮点单元的性能和功能以及 ARM NEON 高级 SIMD 指令集实现,以便进一步提高媒体和信号处理功能的速度。 MPE 扩展 Cortex-A5 浮点单元 (FPU),提供一个附加暂存器集,在 8 位、16 位和 32 位整型以及 32 位浮点数据类型的基础上支持一组丰富的 SIMD 操作。 |

浮点单元 (FPU) | 可选 Cortex-A5 FPU 是具有 16 个双精度暂存器的 ARM 矢量浮点 v3 体系结构 (VFPv3-D16) 的实现。该单元提供浮点计算功能,符合 ANSI/IEEE 标準 754-1985、二进制浮点运算的 IEEE 标準 (IEEE 754)。 FPU 支持 VFPv3 体系结构中的所有数据处理指令和数据类型,完全支持单精度和双精度加法、减法、乘法、除法、乘累积和平方根运算。它还提供定点和浮点数据格式之间的转换以及浮点常数指令。 |

Jazelle RCT 和 DBX 技术 | 最多可使即时生产 (JIT) 和提前编译的位元组码语言的代码大小缩小 3 倍,同时还支持 Java 指令的直接位元组码执行,以便提高传统虚拟机的速度 |

可配置 L1 高速快取 | 可在 4-64K 範围内单独配置功率最佳化的 L1 指令和数据高速快取。 提供了ARM SRAM 的最佳化实例。 |

高性能AXI汇流排 | Cortex-A5 实现支持多个未决事务的 64 位统一 AXI 汇流排,具有超过 ARM1176JZ-S 的 3 倍记忆体频宽。 |

先进的多核技术 | |

侦测控制单元 (SCU) | SCU 是 ARM 多核技术的中央智慧型单元,负责管理互连、仲裁、通信、高速快取之间的传输和系统记忆体传输、高速快取一致性以及支持所有多核技术的处理器的其他功能。 Cortex-A5 MPCore 处理器也向其他系统加速器和非快取 DMA 驱动的主外设公开这些功能,以便通过共享对处理器高速快取层次结构的访问来提高性能并降低系统範围内的功耗。这一系统一致性还可降低在各个作业系统驱动程式中维持软体一致性所涉及的软体複杂性。 |

加速器一致性连线埠 (ACP) | SCU 上的此 AMBA® 3 AXI™ 兼容的辅助接口为各种系统主机提供了一个互连点,出于总体系统性能、功耗或软体简化的原因,这些接口更易于直接连线 Cortex-A5 MPCore 处理器。 该接口可用作标準的 AMBA 3 AXI 辅助接口,它支持所有标準读写事务,而对连线的组件没有任何其他一致性要求。不过,针对一致的记忆体区域的任何读事务都会与 SCU 互动,以测试所需信息是否已存储在处理器的 L1 高速快取内。如果存储在其中,则会将其直接返回到请求组件。如果未存储在 L1 高速快取中,则在最后转发到主记忆体之前还有机会存储在 L2 高速快取中。 对于针对任何一致的记忆体区域的写事务,在将写入数据转发到记忆体系统之前,SCU 会强制其保持一致性。此外,此事务还可分配到 L2 高速快取,从而消除直接写入对晶片外记忆体产生的功率和性能影响 |

通用中断控制器 (GIC) | 实现最近标準化的、基于架构的 ARM 中断控制器后,GIC 提供了一种强大且灵活的方式,用来进行处理器间通信以及路由系统中断和确定其优先次序。在软体控制下,最多支持 224 次独立中断,每次中断均可在 CPU 之间分布,经过硬体确定优先权,然后在作业系统和 TrustZone 软体管理层之间路由。藉助半虚拟化管理器,此路由灵活性以及支持虚拟化作业系统中断这一特性赋予了增强解决方案功能所需的其中一个主要功能。 |

主要特点

概述

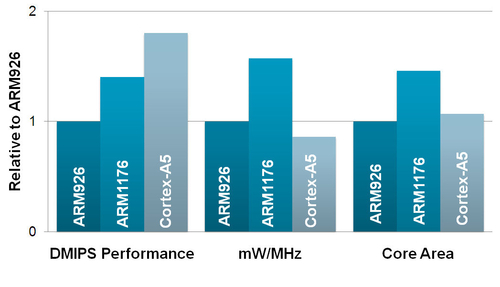

Cortex-A5 处理器可为现有 ARM926EJ-S™ 和 ARM1176JZ-S™ 处理器设计提供很有价值的迁移途径。它可以获得比 ARM1176JZ-S 更好的性能,比 ARM926EJ-S 更好的功效和能效以及 100% 的 Cortex-A 兼容性。

这些处理器向特别注重功耗和成本的应用程式提供高端功能,其中包括:

多重处理功能,可以获得可伸缩、高能效性能

用于媒体和信号处理的可选浮点或 NEON™ 单元

与 Cortex-A8、Cortex-A9 和经典 ARM 处理器的完全套用兼容性

高性能记忆体系统,包括高速快取和记忆体管理单元

套用

Cortex-A5 是为以下套用领域而设计的:需要在极低功耗情况下对高级作业系统进行虚拟记忆体管理。

| 产品类型 | 套用 |

|---|---|

手机 | 入门级智慧型手机、特色手机、移动支付、音频 |

家庭/消费 | 数位电视、DVD |

嵌入式/工业 | MPU、智慧型仪表 |

面积和能效

行业领先的能效是指 Cortex-A5 可以每单位能量完成更多的工作,这意味着可以延长移动设备的电池寿命,减少散热。

Cortex-A5 是最小的 Cortex-A 处理器。

小尺寸:

降低製造成本

允许更多低成本集成

减少泄漏

功耗对比图

功耗对比图兼容性

Cortex-A5 处理器在指令以及功能方面与更高性能的 Cortex-A8、Cortex-A9 和 Cortex-A15 处理器完全兼容 – 一直到作业系统级别。 Cortex-A5 处理器还保持与经典 ARM 处理器(包括 ARM926EJ-S、ARM1176JZ-S 和 ARM7TDMI®)的向后应用程式兼容性。

相关产品

处理器

高通 Snapdragon MSM7227a

高通 Snapdragon MSM7225a

高通 Snapdragon MSM7627a

高通 Snapdragon MSM7625a

高通 Snapdragon MSM8225

高通 Snapdragon MSM8625

高通 Snapdragon MSM8X25Q

韩国Telechips TCC8923

手机产品

摩托罗拉XT615、XT681,海信U8,HTC T328w(风)、HTC新渴望T328D,华为U8818,华为U8825D(Ascend G330D),华为C8825D(Ascend G330C),中兴V889D,摩托罗拉XT535 Defy,联想A780,酷派7260+,海尔N86W ,TCL A988,飞利浦W635等。

读书笔记摘抄新闻资讯

读书笔记摘抄新闻资讯